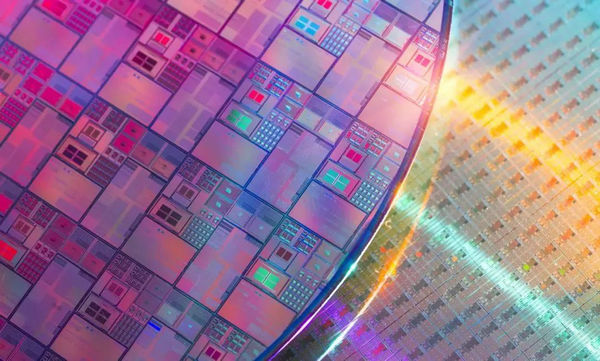

芯片载体材料:Chipcarrier,亦称为封装载板或封装基板,是IC的关键材料,

焊盘以周边阵列形式分布在芯片表面,单个I/O可达1000个,最小焊盘节距40

相比于WB技术,具有优异的电学性能和热学性能,可支持更高的I/O数,封装

缩短互连长度,降低电阻,减小RC延迟,改善电学性能。散热j6国际性好,降低热阻。

日本揖斐电株式会社(Ibiden)、新光电气工业株式会社(Shinko)、京瓷集团(Kyocera)为

1.陶瓷基板:最初选用材料,支持较高密度I/O,性能稳定,热膨胀系数与硅接近,

优点:价格低、综合性能好、气密性好、可靠性好,热导率仅为20W/m·K,介

电常数约为10,需要改良。易实现多层化,主要用于高速器件封装,如高频器件输入

是高密度、大功率电子封装理解载陶瓷板。应用于高频器件,高亮LED,半导体激光

SiC,机械强度仅次于金刚石,具有优良耐磨性和耐腐蚀性,热导率同于Cu,CTE与

2.金属基板:以Al、Cu、Fe、Mo等金属板基板,在基材上制造绝缘层和

片级封装。WB-BGA,通用芯片封装;FC-BGA,处理器及南北桥芯片;

复合制成。BGA、CSP、COF,产品LED/LCD,触控屏、计算机硬盘、光

4.硅/玻璃基板(中介转接层):基于封装通孔TPV的Interposer,可实现个芯片之间互

连和再布线,将芯片IO数减少后再连接到传统基板或PCB上。用于GPU、FPGA、

分为硅、玻璃及有机体系三类。要求高热导率、低CTE、低介电常数。硅、玻璃转接

硅中介层优点:可埋电阻及有源器件,可通过掺杂使其起到接地作用,省去金属化,

玻璃中介层优点:绝缘材料,省去绝缘层工艺且高频传输更优、CTE可调、成型性好、

精减薄:CMP技术,削除应力,60 mm/min,粗糙度小于0.1 mm。

CMP去除介质工艺:刻蚀技术,使TSV内部铜柱相对于硅衬底凸出(2~10 mm ),利用

PECVD沉积介质层,CMP或刻蚀技术将TSV上方沉积介质层去掉,暴露铜柱。铜污染相

无铜污染刻蚀去除介质层工艺:刻蚀技术,使TSV内部铜柱相对于硅衬底凸出(2~10

mm ),利用低温PECVD沉积介质层并旋涂光刻胶,利用背部光刻技术对光刻胶开窗。

减薄去除介质层工艺:TSV底部介质层在减薄中去除,刻蚀技术,使TSV内部铜柱相对于

硅衬底凸出(2~10 mm ),利用低温PECVD沉积介质层,利用CMP或刻蚀技术将TSV上

方沉积介质层去除,直接将TSV抛光到同一高度。硅会被铜污染,导致器件失效。

湿法刻蚀:化学试剂(HF、HCl、IPA)反应,各向同性,尺寸大,深宽比小。

联;日本Asahi Glass用铜膏进行玻璃孔填充;泰库尼斯科公司和NEC

减成工艺制造成本低,工艺成熟、稳定、可靠,适用于大规模生产对线mm以上)的基板产品,目前应用十分广泛。

感光抗蚀分辨力和抗蚀层厚度密切相关。厚度越j6国际小,越容易实现精细布线mm的干膜比较困难,采用湿膜工艺可以制造出5mm的厚膜,但湿

Copyright © 2014-2026 j6国际科技有限公司 版权所有 陕ICP备2021015203号-1 j6国际官方网站